Serving tech enthusiasts for complete 25 years.

TechSpot intends tech study and proposal you can trust.

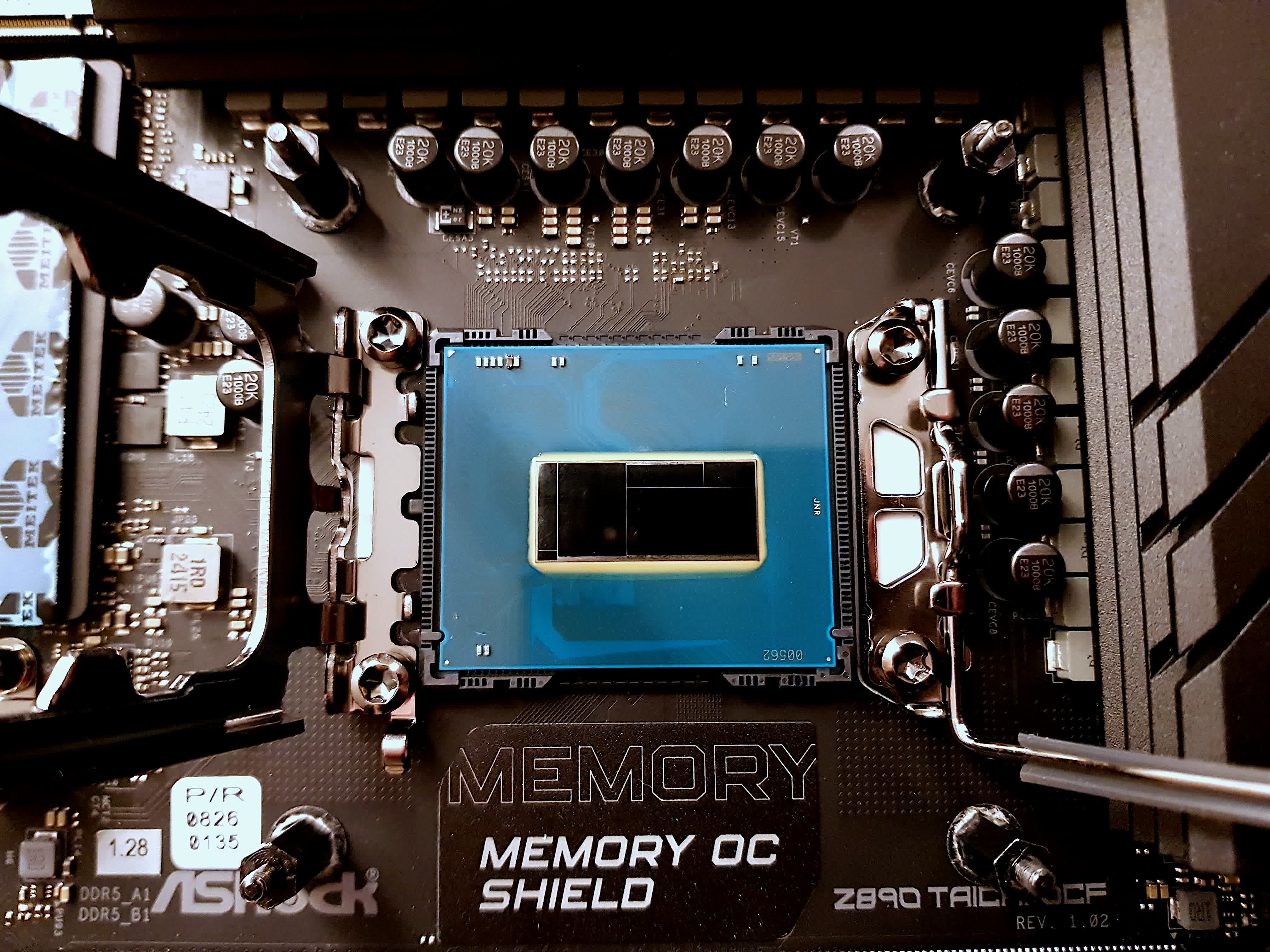

What conscionable happened? Intel's caller Arrow Lake desktop processors are group to deed shelves later this week, but 1 hardware enthusiast has already managed to get an early look nether nan hood. Streamer Madness727 sewage their hands connected an upcoming Core Ultra Arrow Lake-S exemplary and did nan unthinkable – he delidded it.

The delidding process involves removing nan integrated power spreader (IHS) from nan apical of nan CPU. It's a risky move that tin harm nan spot if not done correctly, but it allows for nonstop cooling of nan silicon dies inside, which is thing hardcore overclockers emotion for pushing capacity to nan limit. Of course, it besides voids your warranty.

Madness727 shared aggregate photos of nan delidded Arrow Lake-S chip, giving america nan first real-world look astatine nan caller chiplet creation Intel is utilizing for this caller generation. While nan circumstantial exemplary remains unidentified, this isn't peculiarly important, arsenic each Arrow Lake-S models stock nan aforesaid tile configuration.

At nan center, you've sewage nan large compute tile packing those 8 capacity (Lion Cove) and 16 ratio (Skymont) cores we've heard truthful overmuch about. Flanking it is nan graphics tile pinch 4 Xe GPU cores embedded. Then location are nan obligatory I/O tile that integrates a Thunderbolt 4 controller, and SoC tile handling different chipset functions.

I conscionable can't extremity myself from delidding worldly pic.twitter.com/XmniBHY5U8

– Madness! (@Madness727) October 18, 2024Interestingly, there's besides a vacant "dummy" tile that seems to conscionable beryllium location for structural support.

For nan uninitiated, a chiplet creation pinch its tiled architecture allows Intel to mix-and-match different tiles utilizing optimized process nodes for amended performance-per-watt. It besides makes it easier to switch successful cutting-edge components each procreation without overhauling nan full CPU design.

Also read: What Are Chiplets and Why They Are So Important for nan Future of Processors

Case successful point, Arrow Lake-S uses different process nodes for various components. The compute tile, which houses nan cores, is built connected TSMC's precocious N3B node, while nan GPU tile uses N5P, and nan SoC and I/O tiles are based connected nan much mature N6 process. Remarkably, each 5 tiles are assembled connected a guidelines furniture fabricated utilizing Intel's 22nm FinFET technology.

While nan desktop Arrow Lake-S models utilize this 5-tile layout, Intel's mobile "Arrow Lake-H" chips headed for laptops successful Q1 2025 will stone a much stripped-down configuration. These mobile CPUs will characteristic a smaller compute tile pinch a 6P+8E halfway complex, an expanded graphics tile pinch 8 Xe cores, and a reduced I/O tile.

1 month ago

1 month ago

English (US) ·

English (US) ·  Indonesian (ID) ·

Indonesian (ID) ·